Majid Dadafshar, Principal Engineer Field Application Engineering en ON Semiconductor nos enseña cómo controlar la integridad de señal en nuestros diseños y aplicaciones.

Síntesis del artículo

La integridad de señal es unos de los principales aspectos que abordan muchos profesionales en el diseño de los circuitos digitales de alta velocidad. La integridad de señal conlleva la degradación de calidad y los errores de sincronización de las formas de onda de la señal digital, ya que las señales recorren su camino desde el transmisor al receptor a través de interconexiones como estructuras de encapsulado, trazas de PCB, vías, cable flexible y conectores.

Los diseños de bus de alta velocidad actuales como LpDDR4x, USB 3.2 Gen1/2 (5 Gbps/10 Gbps), USB3.2×2 (2×10 Gbps), PCIe y el próximo USB4.0 (2×20 Gbps) experimentan una degradación de señal cuando los datos de alta frecuencia circulan desde el transmisor al receptor.

Este artículo pretende ofrecer un resumen que cubra los fundamentos de la integridad de señal y elementos importantes como el skin effect, la adaptación de impedancia (impedance matching), la impedancia característica o la reflexión para sistemas de datos de alta velocidad.

Introducción

A medida que los nodos de silicio soportan un proceso de 10, 7 e incluso 5 nm, es posible aumentar la integración y la funcionalidad en un tamaño de chip dado. En las aplicaciones móviles, la tendencia se dirige hacia una mayor frecuencia y una ratio de datos alta con la intención de optimizar la disipación de potencia al reducir las tensiones del núcleo operativo a 0,9 V, 0,8 V, 0,56 V o incluso menores.

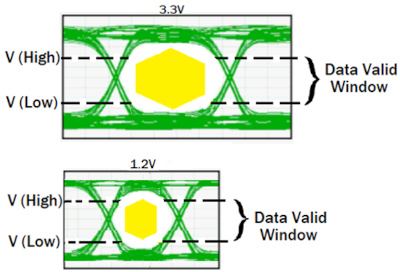

La operación en una frecuencia superior con tensiones operativas inferiores hace que los niveles de umbral o la ventana válida de datos para unos datos de bit dados sean mucho más pequeños en el rango que impacta, tanto en la distribución de energía a través de las trazas y los planos de energía como en el cierre de la apertura del “Ojo” (“Eye”).

El eye closer causado por una operación de mayor frecuencia y menor tensión incrementa la posibilidad de error en la transmisión de datos, aumentando la tasa de error binario (Bit Error Rate) en la que se requiere la necesidad de retransmitir el flujo de datos.

Esta retransmisión provoca que el procesador tenga que estar en modo activo durante un largo periodo de tiempo para poder retransmitir dicho flujo de datos que, a su vez, causa una mayor disipación de potencia y disminuye de manera eficaz el Day Of Usage (DOU) en aplicaciones móviles.

Al incorporar otros retos de diseño como la atenuación de señal, la reflexión, la adaptación de impedancia o la inestabilidad en un diseño de elevada frecuencia dado, entonces, quedará claro cómo las pérdidas de señal dificultan que el receptor interprete la información correctamente, lo que aumenta la posibilidad de error.