ANSYS presenta la versión 2014 de RedHawk, la plataforma de análisis de ruido y fiabilidad estándar para diseños basados en FinFET. La nueva versión ofrece un mayor rendimiento, capacidad y cobertura, así como la precisión de cierre de sesión para hacer frente a los retos que afronta la creciente complejidad de los diseños basados en FinFET.

Para satisfacer las demandas de menor consumo de energía y mayor rendimiento operativo en los actuales móviles, equipos informáticos, electrónica de consumo, de automoción y circuitos integrados (IC), los diseñadores están adoptando la tecnología FinFET, una arquitectura de transistor tridimensional en la que el canal ascendente está envuelto por un electrodo. Mientras que FinFET ofrece muchos beneficios, estos diseños basados en la plataforma de análisis de ruido y fiabilidad tienen pequeños márgenes de ruido y fiabilidad, que requieren un control más estricto sobre la precisión del análisis.

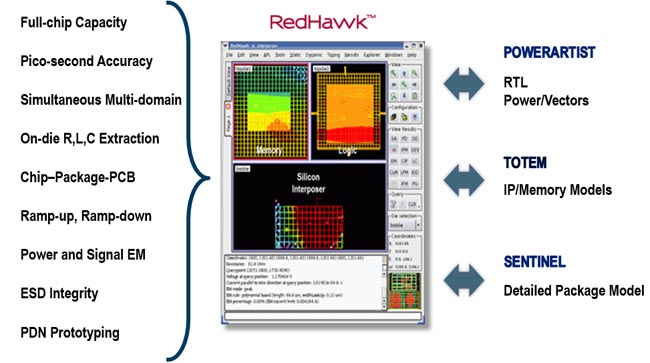

Capacidad y rendimiento para la plataforma de análisis de ruido y fiabilidad

Para cumplir con la calidad del cierre de sesión, el análisis SOC (System-On-Chip) de caída de tensión dinámica necesita un marco de modelado plano para predecir con precisión el flujo de corriente dentro de los elementos altamente acoplados tanto en el chip, el paquete y el circuito impreso (PCB). Debido a la naturaleza global de la red de suministro de energía, un enfoque jerárquico más tradicional no puede ofrecer la precisión necesaria para el cierre de sesión. La versión 2014 de RedHawk incluye funciones de procesamiento en equipos distribuidos (DMP, o Distributed Processing Machine) que ofrecen, de media, una mejora de tres veces en el impacto en la memoria, lo que permite la simulación de más de 100 millones de casos o más de 2.000 millones de nodos, manteniendo la precisión de la simulación plana. La arquitectura propietaria de DMP aprovecha la mayor potencia de procesamiento y la capacidad de memoria disponible en un clúster privado para simular cada módulo en el contexto del chip completo, incluyendo elementos del paquete y PCB.

Además de DMP, esta versión incluye cambios en la arquitectura de software y optimizaciones de flujo para mejorar entre dos y tres veces el tiempo de ejecución respecto a la versión anterior, que ya era la solución más rápida del mercado para la integridad de potencia. La combinación de DMP y las mejoras en la arquitectura ofrecen la capacidad y el rendimiento necesarios para los actuales diseños de gran tamaño, especialmente los fabricados utilizando tecnologías FinFET, sin que afecte a la precisión de cierre de sesión.

Análisis conjunto de chips y paquetes

Con sistemas SoC cada vez más grandes, además de las variaciones en la corriente alterna y en el perfil parasitario a través del chip, la conexión entre el SoC y el paquete tiene que ser tan granular como sea posible para ofrecer un cierre de sesión de calidad. La plataforma de análisis de ruido y fiabilidad RedHawk versión 2014 incluye RedHawk-CPA, la primera solución integrada para la simulación y análisis conjunto de chips y paquetes. Esta nueva opción mapea el paquete hasta el esquema, a través de la conectividad física pin a pin, fusionando sin problemas una red parasitaria de paquetes totalmente distribuida con una red de distribución de potencia en el chip. Mediante la incorporación tanto de chips y como de esquemas de paquetes en el mismo entorno de simulación, RedHawk-CPA proporciona información inmediata sobre la calidad del diseño del paquete, así como el impacto de los paquetes parasitarios en el rendimiento del chip.

Fiabilidad con certificación Foundry

Los diseños basados en FinFET tienen menores límites de electromigración (EM) y un nuevo conjunto de reglas de EM, así como un mayor impacto térmico en la fiabilidad EM. La plataforma de análisis de ruido y fiabilidad RedHawk cuenta con certificación Foundry para el análisis de caída de potencia y de EM de la última tecnología de proceso. Es compatible con normas EM avanzadas que tienen en cuenta la dirección del flujo de corriente, la topología del metal y los tipos de vía tanto para redes de potencia como para redes de señal. Además, esta versión permite análisis EM térmicos ofreciendo un modelo térmico de chips (CTM) que captura con precisión la distribución térmica que es crítica en los dispositivos FinFET con mayores problemas de auto calentamiento.