Martin Kellerman, director de marketing en Microchip Technology, nos explica cómo crear fácilmente nodos Cool Running Edge de alto rendimiento en FPGAs.

Con los nodos Edge, uno de los principales criterios suele ser el bajo consumo de energía, pero ¿por qué importa esto y cuáles son las implicaciones?

Es posible que algunos desarrolladores de aplicaciones no reconozcan esto como un problema, ya que sus dispositivos funcionan con alimentación por cable, pero esa no es toda la historia.

Un menor consumo de energía también significa un menor autocalentamiento del dispositivo; esto significa que la FPGA o el dispositivo semiconductor que ejecuta el nodo perimetral se mantendrá más frío, evitando la necesidad de un ventilador, que es un componente que es conocido por fallar.

Menos componentes significan un tamaño físico más pequeño y que puede caber en un gabinete más pequeño (toda una ventaja hoy en día).

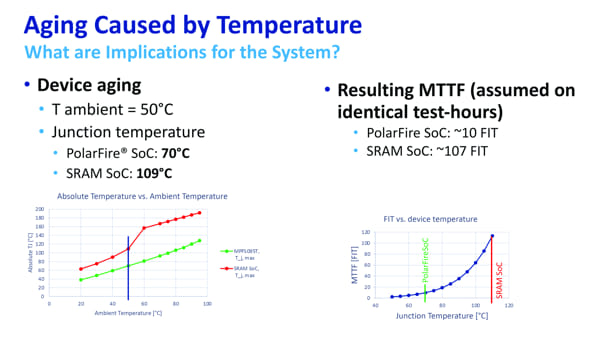

Otra consideración es que las FPGAs son semiconductores y, si se calientan, esto también puede reducir la vida útil de los dispositivos. Mantenerlos más fríos proporciona un tiempo medio más prolongado hasta el fallo y una tasa de FIT más baja.

Una regla general en la industria de los semiconductores es que, si se reduce la temperatura de la unión en aproximadamente diez grados, también se reduce aproximadamente a la mitad la tasa FIT.

Hasta cierto punto, es una compensación entre un menor consumo de energía y, por lo tanto, una vida más larga, con una determinada cantidad de características, o un mayor consumo de energía que permite características adicionales en el diseño.

Una tasa de FIT más baja en el hardware, debido a un menor consumo de energía y una temperatura más baja, también facilita la obtención de la certificación del dispositivo.

Eficiencia significa longevidad

¿Cuál es la arquitectura detrás de la eficiencia energética y por qué es realmente importante?

Al comparar las FPGA de Microchip con las FPGA típicas, las FPGA de Microchip se basan en tecnología no volátil. Esto significa que el flujo de bit y la configuración de la FPGA, se almacenan directamente en las celdas activas; esto siempre se encuentra dentro de la FPGA y no se pierde cuando se apaga. La próxima vez que lo encienda, la configuración estará disponible inmediatamente.

En los dispositivos SRAM, las celdas deben recargarse continuamente y también sufren algunas fugas, lo que provoca el autocalentamiento. Para dispositivos de tamaño similar, las FPGAs suelen utilizar alrededor del 50 % del consumo de energía de las arquitecturas alternativas.

La tecnología no volátil de los FPGA de Microchip también brinda inmunidad contra perturbaciones de eventos únicos, como impactos de neutrones y otros impactos de partículas que pueden cambiar la funcionalidad del FPGA. Esto elimina la necesidad de esquemas de mitigación requeridos por otras tecnologías.

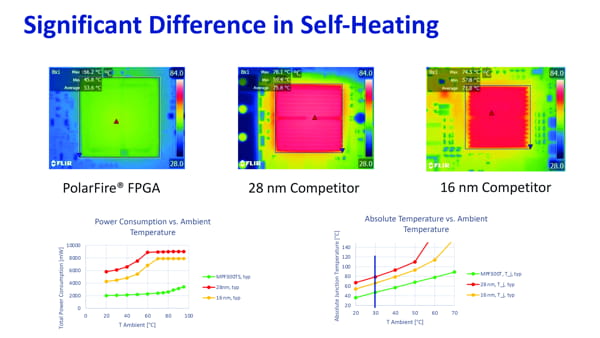

Si observamos la misma aplicación, la misma complejidad de FPGA y el mismo diseño en tres FPGA diferentes, a la izquierda del diagrama, vemos el modelo FPGA PolarFire. Los otros dos modelos son FPGA de otras marcas en los que tenemos el mismo diseño, la misma cantidad de tablas de consulta, y los mismos bloques, que se ejecutan en una placa FPGA de tamaño similar y a la misma temperatura ambiente.

En las pruebas térmicas, las estimaciones fueron de alrededor de +45 °C para PolarFire, alrededor de +65 °C para el dispositivo de 16 nm y alrededor de +70 a +80 °C para el competidor de 28 nm.

¿Qué implica eso para el tiempo medio antes de la falla?

Consideremos un diseño que ejecuta uno de nuestros sistemas SoC y comparémoslo con un SoC basado en SRAM. Con el mismo diseño, el mismo barrido de temperatura y el consumo de energía registrado, se muestra, a continuación, la curva de tiempo promedio hasta la falla para cada uno. El SoC PolarFire a una temperatura ambiente de +50 °C alcanza unos +70 °C y el sistema basado en SRAM alcanza unos +110 °C.

Para el SoC basado en SRAM, que alcanza los 110 °C, la tasa de FIT sería de alrededor de 107. Mientras, el SoC PolarFire con sus +70 °C de temperatura de unión muestra solo unos diez FIT, por lo que esos diez grados de más hacen una diferencia significativa en la tasa FIT. Esta disparidad en las tasas de FIT hace una diferencia significativa en la fiabilidad del dispositivo en el campo.