Normalmente, los conectores SMA de montaje en PCB han sido utilizados para dividir las señales de transmisión y recepción en los transceptores.

Este enfoque ha sido utilizado durante décadas. La cantidad de transceptores por circuito integrado era baja y los conectores SMA podían soportar ratios de datos de Megabit y pocos Gigabit por segundo. Como las velocidades de transceptor han superado los 10 Gbps, se ha desarrollado otro tipo de conectores para respaldar ratios de hasta 20 Gbps. Sin embargo, esto supone un nuevo reto para la Ley de Moore.

Como los circuitos integrados también han conseguido ser más densos con nodos de proceso cada vez más compactos (90 nm -> 65 nm -> 45 nm -> 28 nm -> 20 nm -> 16 nm ->), los fabricantes de ASIC, FPGA y ASSP han aumentado el número de transceptores en sus semiconductores. Por ejemplo, Xilinx tiene previsto incluir hasta 76 transceptores en sus Zynq UltraScale+ MPSoC y hasta 128 en sus Virtex UltraScale+ FPGA.

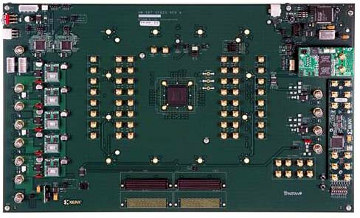

Las tarjetas de caracterización para estos dispositivos requerirían cientos de conectores SMA, por lo que el tamaño de PCB y las restricciones de coste limitan el uso de los mismos. Además, se necesitan distribuciones de PCB más complejas.

Por todas estas razones, Samtec ha desarrollado los puntos de test para caracterización de transceptor denominados Bulls Eye Test Point System como una alternativa para reemplazar SMA en sistemas de test y medida. Ayudan a reducir el espacio de tarjeta y las longitudes de traza, así como a mejorar el rendimiento y disminuir el coste.

Los diseños de alta densidad cuadriplican las señales de ancho de banda en el mismo estado que los conectores SMA. El nuevo sistema de puntos de test está disponible en versiones mono-puerto o multi-puerto o como conector ganged.

Usos de los nuevos puntos de test para caracterización

Bulls Eye Test Point System ha encontrado un nuevo ámbito de aplicación en tarjetas de caracterización, evaluación y desarrollo de FPGA.

Los puntos para test se caracterizan por trabajar en una frecuencia de 20 GHz con impedancia de 50 Ω, cierre mecánico de tipo bayoneta y construcción de cable dieléctrico sólido.