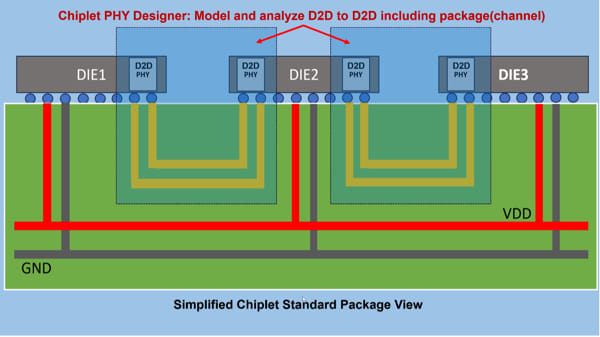

Para asegurar la interoperabilidad y rendimiento óptimo en diseños de circuitos integrados heterogéneos y en 3D, el diseñador PHY de Chiplet para simulación D2D con estándar UCIe permite realizar la verificación de conformidad con las especificaciones de este último estándar.

Keysight Technologies, compañía centrada en las herramientas de diseño y simulación digital de alta velocidad, anuncia el lanzamiento de su nuevo diseñador PHY de Chiplet para simulación D2D con estándar UCIe.

Esta herramienta de automatización de diseño electrónico (EDA) se posiciona, según indican desde Keysight, como la primera de la industria capaz de proporcionar capacidades detalladas de modelado y simulación para la interconexión de chiplet a chiplet (D2D), un componente esencial en la comprobación del rendimiento de diseños integrados en circuitos heterogéneos y 3D, comúnmente conocidos como chiplets.

Su relevancia se centra en asegurar que los diseños cumplan con las especificaciones del estándar Universal Chiplet Interconnect Express (UCIe).

Dicho estándar abierto define la interconexión entre chiplets dentro de un encapsulado avanzado 2.5D o 3D. Actualmente, se encuentra en proceso de ser soportado o adoptado por una amplia gama de proveedores de equipos de semiconductores, herramientas de EDA, fundiciones y diseñadores de chiplets.

Tres características principales

Para empezar, las características clave del simulador de la capa física del Diseñador PHY de Chiplet incluyen el soporte al estándar de capa física UCIe, que permite llevar a cabo el análisis automatizado de señales, siguiendo convenciones de nomenclatura estándar, conexiones automáticas entre múltiples dados a través de interconexiones de paquetes, configuración de simulación dirigida por estándares como el grado de velocidad, y configuración de mediciones intuitiva a través de un componente de sonda especializado.

Mientras, también incluye la medición de la función de transferencia de voltaje (VTF), con un cálculo preciso de una VTF para asegurar el cumplimiento de las especificaciones de UCIe y análisis de la tasa de error de bits (BER) del sistema hasta niveles de 1e-27 o 1e-32, así como la medición de la altura del diagrama de ojo, ancho de ojo, sesgo, margen de máscara y contorno de BER.

Y, finalmente, tenemos el análisis de reloj adelantado, que ofrece una captura precisa del comportamiento de reloj asincrónico.

En el “Servicio al lector de NTDhoy” puedes solicitar más información sobre el diseñador D2D.