Menta ha anunciado una familia de cores IP eFPGA embebidos off-the-shelf predefinidos que dotan de un “nuevo nivel de flexibilidad” para crear dispositivos System on Chip (SOC) complejos. Estos cores IP eFPGA (embedded FPGA), optimizados para proceso de 28 nm, se combinan con la herramienta Origami Programmer EDA de la compañía para ayudar a los diseñadores a realizar cambios post-fabricación de forma fácil y rápida.

La solución completa de Menta responde a la creciente necesidad de mejoras en capacidad de programación de SOC complejos. Al integrar un tejido FPGA como un core IP en un SOC, los diseñadores de semiconductores y los fabricantes de equipos actualizan el silicio en la post-producción, eliminando así el coste y el tiempo asociados a re-spinning.

Ya se trate de implementar una función específica o cambiar un estándar en evolución, la alternativa de Menta con sus nuevos cores IP eFPGA embebidos off-the-shelf permite configurar los SOC en una amplia variedad de aplicaciones en defensa (e industria aeroespacial), automoción, entornos industriales y consumo.

Opciones para los cores IP eFPGA embebidos off-the-shelf

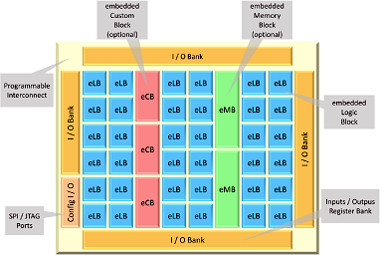

Esta familia de cores IP incluye seis nuevas opciones eFPGA de 4 a 60k puertas ASIC equivalentes, así como bloques DSP. Los cores IP están desarrollados como hard macros con tamaños de array optimizados para bloques lógicos embebidos (eLB), bloques a medida embebidos (eCB) y bloques de memoria embebidos (eMB), cada uno de los cuales se puede personalizar en tipo, número y tamaño para adecuarse a las necesidades de varios mercados.

Los eFPGA IP cores han sido diseñados para ofrecer compatibilidad de test estándar con todas las soluciones de prueba ASIC y SOC (cobertura del 99.8 por ciento).

Los cores IP eFPGA embebidos off-the-shelf se suministran con una herramienta EDA que soporta desde diseño HDL a bitstream con síntesis, mapping, place & route. La tecnología eFPGA se basa en las cadenas Origini, que ahora incluyen síntesis para aplicaciones RTL en VHDL, Verilog o SystemVerilog, así como soporte SDC.

También están disponibles herramientas de análisis de sincronización para facilitar el proceso de diseño.