VPD puro: el desafío del almacenamiento de energía, la ganancia de corriente y la densidad de corriente

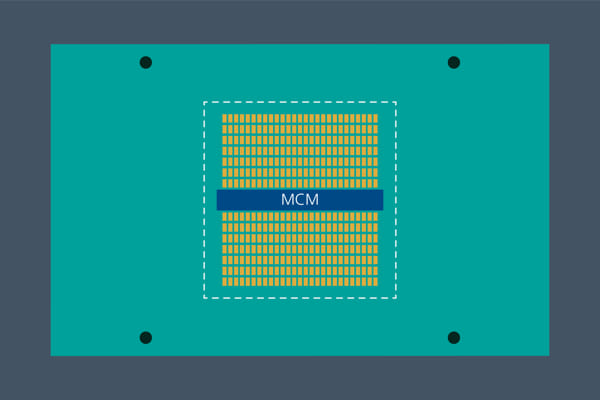

Para lograr una entrega vertical pura para los rieles de alimentación del núcleo de alta corriente en este ejemplo, se requeriría un aumento en la densidad de corriente VR de 3 veces o más, de aproximadamente 1 A / mm2 a aproximadamente 3 A / mm2 (para una huella típica de paquete de procesador de entrenamiento de 3,500 mm2), lo que permite que quepa dentro de la matriz de condensadores de derivación (Figura 5).

Lograr este aumento multiplicativo en la densidad de corriente exige un replanteamiento completo del enfoque tradicional de realidad virtual, incluido el paquete del módulo de potencia.

El desafío general con el aumento de la densidad de corriente de PoL VR es el tamaño de los componentes magnéticos necesarios para el almacenamiento de energía. Las arquitecturas VR multifásica y VR de inductor acoplado (regulación de voltaje transinductor o TLVR) se basan en el almacenamiento de energía en componentes magnéticos (inductores o transformadores respectivamente) y la transferencia de la energía almacenada (como corriente) al procesador.

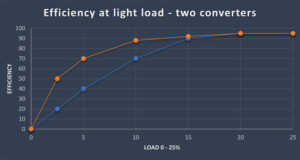

Los módulos de potencia recientemente introducidos de esta variedad tienen especificaciones de frecuencia de conmutación y corriente de salida modestamente más altas, y son más compactos, con dos etapas de fase moduladas por módulo de potencia. Estos componentes generalmente regulan desde 12 VIN, alimentados por convertidores de bus de relación fija de 48 V (K = 1/4).

Los enfoques alternativos utilizan MOSFET laterales de menor voltaje (generalmente 6 VIN) que se conmutan a frecuencias algo más altas, lo que reduce el tamaño de los inductores de almacenamiento de energía.

Estos VR PoL de menor voltaje de entrada son alimentados por convertidores de bus de 48 VIN a 6 VOUT (K = 1/8), que emiten niveles de corriente mucho más altos, alrededor de 160 Amperios, lo que aumenta desfavorablemente las pérdidas de potencia del bus intermedio en la PCB (W/PCB).

Debido a los límites físicos en la frecuencia máxima de conmutación, incluso a 6 V, los enfoques multifásicos y TLVR tradicionales alcanzan una densidad de corriente máxima de alrededor de 1 A / mm2. Ambas topologías dan como resultado módulos de potencia que son altos (de 4 a 8 mm) y relativamente pesados, en gran parte debido a los componentes magnéticos (típicamente ferríticos) de almacenamiento de energía.

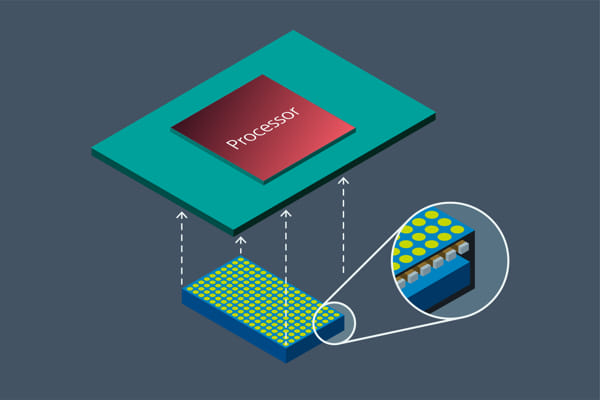

Otro enfoque temprano, introducido por Vicor en 2016, integró la matriz de condensadores de derivación en un módulo de potencia apilado, como se muestra a continuación (Figura 6). Una capa adicional de «caja de cambios» asignó la energía a la matriz de cuadrícula de bolas del procesador, lo que convirtió a cada modelo de dispositivo en una solución personalizada. Este método presenta desafíos de escalabilidad y costo en comparación con una familia de productos estándar.

La conmutación a frecuencias significativamente más altas (más de 1 MHz) reduce el tamaño de los componentes del almacenamiento de energía. Sin embargo, para los VR reductores multifásicos o TVLR, este enfoque requiere reducir el voltaje de funcionamiento de los interruptores MOSFET de potencia.

La arquitectura FIVR heredada es un ejemplo clásico, donde para evitar el problema de la densidad de la tarjeta PCB del condensador de derivación, los reguladores reductores de obleas de silicio que conmutan a velocidades de MHz pudieron alcanzar las densidades de corriente necesarias.

Las CPU de servidor en ese momento usaban un voltaje de suministro fuera del chip de 1.8 VEXT y, por lo tanto, una ganancia de corriente de solo 2x (1.8 VEXT / 0.85 core VDD) resultado del enfoque FIVR. Se informó que la eficiencia estaba en el rango del 80%. (7) (8)

Para un procesador de entrenamiento genAI TDC de 1.000 a 2.000 Amperios, se necesitan mayores ganancias de corriente y mayores eficiencias que logren evitar pérdidas térmicas excesivas. En las arquitecturas VR de 12 y 6 V citadas anteriormente, las ganancias de corriente están en los rangos de 20x y 10x, respectivamente (para un procesador VDD de núcleo de 0,7 V).

Pero con las 30 o más fases moduladas necesarias para el rail central, estas arquitecturas no alcanzan la densidad de corriente requerida de 3 A / mm2 que permitirían la colocación de VR incrustada dentro del campo de la matriz de condensadores de derivación.